Published:

Updated:

Updated:

VHDL IP: PS2

Block description

| Port | DIR | Type | Description |

|---|---|---|---|

| reset | I | signal | Asynchronous reset |

| clk | I | signal | Clock signal, must be x4 faster at least than kbclk |

| kbdata | I | signal | PS2 serial data |

| kbclk | I | signal | PS2 data clock (~15 kHz) |

| newdata | O | signal | One clk cycle pulse, to raise an interrupt in PicoBlaze for example |

| do | O | 8-bit bus | Byte sent by PS2 device |

When a new data is available in do, a pulse (one clock cycle pulse) is sent by newdata

signal notifying the host circuit to transfer the octet to a FIFO buffer or something else. System

clock clk must be faster (x4 or more) than kbclk (kbclk is about 15

kHz).

Synthesis report

| Device | xc3s400-4ft256 |

| Slices | 28 |

| FFs | 44 |

| LUTs | 31 |

| IOBs | 13 |

| GCLK | 1 |

| Maximun clock frequency | 178.859 MHz |

Simulation

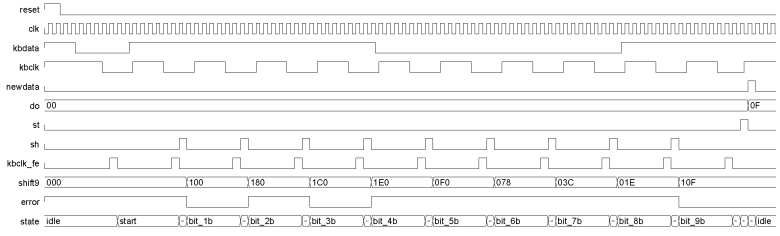

Cronogram in ModelSim for transmision of character 0x0F from keyboard to host

Download

Files:

- interface_ps2.vhd

- utils.vhd

- interface_ps2_test.vhd Test Bench. Simulate it for 200 ns at least.

References

- The PS/2 Mouse/Keyboard Protocol

- "Diseño digital con lógica programable", 1º edición, Luis Jacobo Álvarez Ruiz de Ojeda, Tórculo Edicions, ISBN 84-8408-301-2